Dan NICULA

ELECTRONIC

˘

A DIGITAL

˘

A

Carte de ˆınv˘at¸˘atur˘a 2.0

Editura Universit˘at¸ii TRANSILVANIA din Bra¸sov

ISBN 978-606-19-0563-8

2015

Lect¸ia 17

Registre ¸si num˘ar˘atoare

17.1 Not¸iuni teoretice

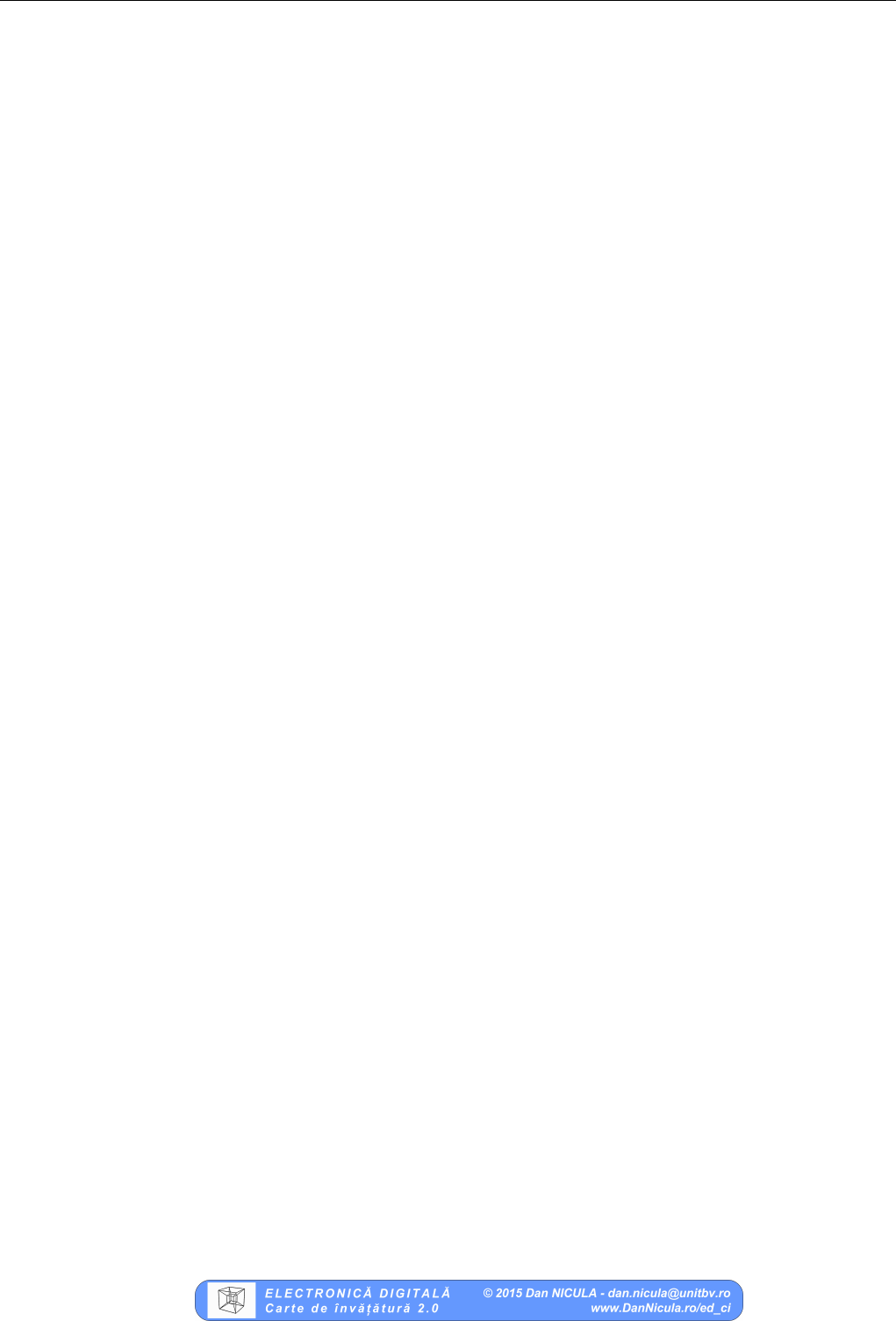

Extensia paralel a unui bistabil poart˘a numele de registru. Simbolul bloc ¸si structura unui registru de 4 bit¸i imple-

mentat cu bistabile D sunt prezentate ˆın figura 17.1.

Figura 17.1 Registru D: simbol bloc ¸si structur˘a.

ˆ

In funct¸ie de modalitatea de ˆınc˘arcare ¸si accesare a datelor, registrele se clasific˘a astfel:

• Registru paralel-paralel. Datele sunt ˆınc˘arcate ˆın registru ¸si accesate din exterior ˆın paralel. Fat¸˘a de registrul

”clasic”, registrul paralel-paralel poate dispune de o intrare suplimentar˘a care valideaz˘a ˆınc˘arcarea doar cˆand

semnalul de validare este activ (ˆın acest mod, registrul poate ”memora” datele ˆın tot intervalul de timp dintre

dou˘a pulsuri de ˆınc˘arcare).

Tabelul de funct¸ionare este:

LD Q

+

Act¸iune

1 D

ˆ

Incarc˘a starea de pe intrarea de date

0 Q P˘astreaz˘a starea curent˘a

Structura intern˘a (figura 17.2) prezint˘a o bucl˘a ˆıntre ie¸sirea ¸si intrarea registrului intern peste un multiplexor

prin care se selecteaz˘a starea viitoare: se ˆıncarc˘a starea din exterior (LD = 1) sau se ment¸ine starea curent˘a

(LD = 0).

Registrul este utilizat pentru stocarea datelor reprezentate pe mai mult¸i bit¸i ˆıntre dou˘a activ˘ari succesive ale

semnalului de ˆınc˘arcare (ˆınc˘arcarea nu trebuie s˘a se fac˘a la fiecare front activ al ceasului, ca ˆın cazul registrului

clasic).

• Registru paralel-serie (de serializare). Datele sunt ˆınc˘arcate ˆın registru ˆın paralel dar sunt accesate din

exterior ˆın mo d serial. Sunt necesare dou˘a intr˘ari de control pentru determinarea ˆınc˘arc˘arii datelor ¸si a deplas˘arii

acestora ˆın registrul intern (pentru deplasarea serial˘a a datelor pe pozit¸ia accesibil˘a din exterior).

Tabelul de funct¸ionare este:

228 LECT¸ IA 17. Registre ¸si num˘ar˘atoare

Figura 17.2 Registru paralel-paralel cu validare a ˆınc˘arc˘arii.

LD SHR Q

+

Act¸iune

1 X D

ˆ

Incarc˘a ˆın paralel starea de pe intrarea de date

0 1 {S

I

, Q >> 1} Deplaseaz˘a cont¸inutul registrului cu un bit

0 0 Q P˘astreaz˘a starea curent˘a

Structura intern˘a (figura 17.3) prezint˘a o bucl˘a ˆıntre ie¸sirea ¸si intrarea registrului intern peste un multiplexor

prin care se selecteaz˘a starea viitoare: se ˆıncarc˘a starea din exterior (LD = 1), se deplaseaz˘a datele din interior

(LD = 0, SHR = 1) sau se ment¸ine starea curent˘a (LD = 0, SHR = 0). Ie¸sirea serial˘a de 1 bit provine de la cel

mai put¸in seminificativ bit al registrului.

Figura 17.3 Registru paralel-serie (de serializare).

Aplicat¸ia clasic˘a a registrului paralel-serie const˘a ˆın serializarea datelor reprezentate pe mai mult¸i bit¸i ˆın vederea

transmiterii acestora pe un singur fir.

ˆ

In acest caz, un impuls de ˆınc˘arcare LD = 1 este urmat de un num˘ar de

impulsuri de deplasare SHR = 1 egal cu num˘arul de bit¸i ai registrului intern.

• Registru serie-paralel (de deserializare). Datele sunt ˆınc˘arcate ˆın registru ˆın mod serial, dar sunt accesate

din exterior ˆın mod paralel. Este necesar˘a o intrare de control pentru determinarea deplas˘arii datelor ˆın registrul

intern (pentru avansarea serial˘a a datelor acceptate ˆın vederea complet˘arii cuvˆantului de date accesibile din

exterior ˆın paralel). Registrul are o intrare de date de un singur bit.

ˆ

In cazul activ˘arii ˆınc˘arc˘arii datelor, ˆın

pozit¸ia cea mai semnificativ˘a se ˆıncarc˘a datele de intrare S

I

¸si deplaseaz˘a datele interne cu 1 bit. Cel mai put¸in

semnificativ bit se pierde.

Tabelul de funct¸ionare este:

SHR Q

+

Act¸iune

1 {S

I

, Q >> 1}

ˆ

Incarc˘a datele de intrare (1 bit) ¸si deplaseaz˘a cont¸inutul

0 Q P˘astreaz˘a starea curent˘a

17.1. Not¸iuni teoretice 229

Structura intern˘a (figura 17.4) prezint˘a o bucl˘a ˆıntre ie¸sirea ¸si intrarea registrului intern peste un multiplexor

prin care se selecteaz˘a starea viitoare: se ˆıncarc˘a bitul din exterior ¸si se deplaseaz˘a datele (SHR = 1), sau se

ment¸ine starea curent˘a (SHR = 0). Ie¸sirea paralel˘a este accesibil˘a din exterior ˆın orice moment.

Figura 17.4 Registru serie-paralel (de deserializare).

Aplicat¸ia clasic˘a a registrului serie-paralel const˘a ˆın deserializarea datelor reprezentate pe mai mult¸i bit¸i dar

recept¸ionate serial.

ˆ

In acest caz, modulul de control extern trebuie s˘a asigure preluarea datelor ˆın paralel dup˘a

un num˘ar de impuls de ˆınc˘arcare SHR = 1 egal cu num˘arul de bit¸i.

• Registru serie-serie (de deplasare). De¸si ˆın interior exist˘a un registru pe mai mult¸i bit¸i, datele sunt ˆınc˘arcate

¸si sunt accesate serial, cˆate un bit pe tact. Registrul realizeaz˘a o deplasare intern˘a a datelor. Este necesar˘a

o intrare de control pentru determinarea ˆınc˘arc˘arii datelor ¸si a deplas˘arii acestora ˆın registrul intern (pentru

deplasarea serial˘a a datelor acceptate). Registrul are o intrare de date de un singur bit.

ˆ

In cazul activ˘arii

ˆınc˘arc˘arii datelor, ˆın pozit¸ia cea mai semnificativ˘a se ˆıncarc˘a datele de intrare S

I

¸si deplaseaz˘a datele interne cu

1 bit. Cel mai put¸in semnificativ bit se pierde. Ie¸sirea serial˘a de 1 bit provine de la cel mai put¸in semnificativ

bit al registrului.

Registrul se comport˘a ca registrul serie-paralel cu deosebirea c˘a la registrul serie-serie doar un bit (cel mai put¸in

semnificativ) este accesibil din exterior (Q

[0]

).

Tabelul de funct¸ionare este:

SHR Q

+

Act¸iune

1 {S

I

, Q >> 1}

ˆ

Incarc˘a datele de intrare (1 bit) ¸si deplaseaz˘a cont¸inutul

0 Q P˘astreaz˘a starea curent˘a

Structura intern˘a (figura 17.5) prezint˘a o bucl˘a ˆıntre ie¸sirea ¸si intrarea registrului intern peste un multiplexor

prin care se selecteaz˘a starea viitoare: se ˆıncarc˘a bitul din exterior ¸si se deplaseaz˘a datele (SHR = 1), sau se

ment¸ine starea curent˘a (SHR = 0). Ie¸sirea serial˘a (cel mai put¸in semnificativ bit) este accesibil˘a din exterior ˆın

orice moment.

Figura 17.5 Registru serie-serie (de deplasare).

Aplicat¸ia clasic˘a a registrului serie-serie const˘a ˆın stocarea datelor sub forma unei ”cozi de a¸steptare” care

avanseaz˘a doar la comand˘a (SHR = 1).

230 LECT¸ IA 17. Registre ¸si num˘ar˘atoare

Un registru poate avea intr˘ari suplimentare de set sau reset asincrone (care act¸ioneaz˘a prioritar ¸si independent

de semnalul de ceas).

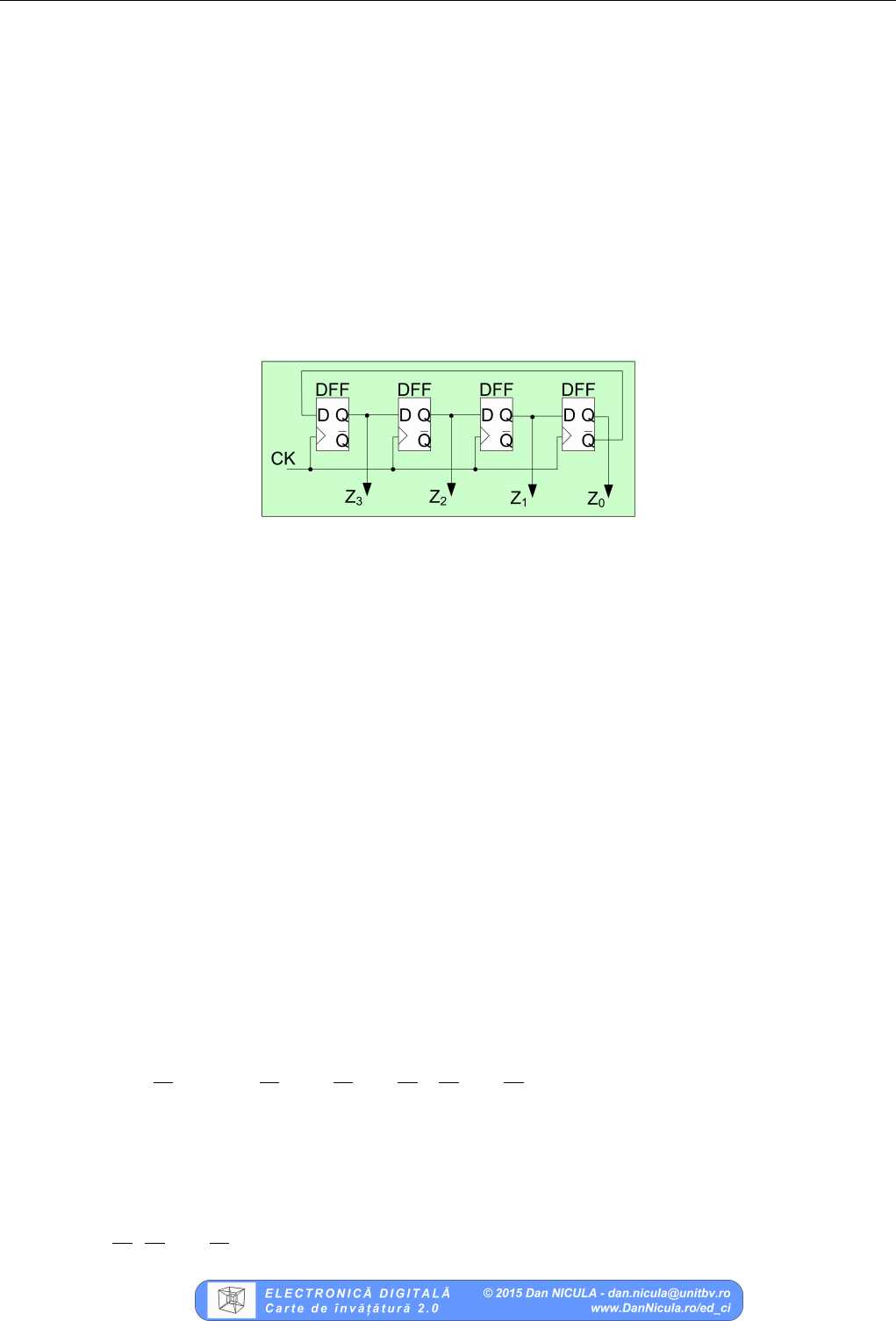

Num˘ar˘atoarele sunt circuite logice secvent¸iale (automate) care ˆı¸si determin˘a starea urm˘atoarea exclusiv pe baza

st˘arii prezente printr-o funct¸ie de num˘arare. Structura ”clasic˘a” a unui num˘ar˘ator sincron (figura 17.6) prezint˘a un

sumator conectat ˆın bucla ˆıntre ie¸sirea ¸si intrarea unui registru de stare. Num˘ar˘atoarele pot avea diverse intr˘ari

care controleaz˘a funct¸ia de num˘arare (direct¸ia de num˘arare, condit¸ia de num˘arare, intervalul de num˘arare, codul de

num˘arare).

Figura 17.6 Schema bloc a num˘ar˘atoarelor sincrone.

Un tip particular de registre ˆıl constituie circuitele LFSR (Engl. ”Linear Feedback Shift Register, Registru de

deplasare cu react¸ie liniar˘a”).

Registrul de deplasare cu react¸ie liniar˘a reprezint˘a o modalitate de obt¸inere a unei secvent¸e de num˘arare lungi cu un

num˘ar mic de bistabile ¸si care s˘a funct¸ioneze la frecvent¸˘a mare.

ˆ

In structura unui LSFR de 4 bit¸i, 3 din cele 4 bistabile

primesc pe intrare semnalul de la ie¸sirea bistabilului de ordin superior. Un singur bistabil, cel mai semnificativ,

prime¸ste la intrare o funct¸ie logic˘a XOR determinat˘a pe baza unor bit¸i mai put¸ini semnificativi. Determinarea bit¸ilor

care intr˘a ˆın calculul valorii viitoare a bitului cel mai semnificativ se face pe baza unui polinom. Polinomul are

gradul egal cu num˘arul de bit¸i ai LFSR ¸si prezint˘a indec¸sii bit¸ilor care concur˘a la determinarea valorii viitoare a celui

mai semnificativ bit. De exemplu, dac˘a polinomul este X

4

+ X

3

+ 1, figura 17.7, valoarea viitoare a bitului cel mai

semnificativ este determinat˘a prin funct¸ia XOR ˆıntre bitul 0 ¸si bitul 3. Se remarc˘a urm˘atoarele:

- Funct¸ia XOR realizeaz˘a funct¸ia de adunare aritmetic˘a a bit¸ilor.

- Pentru N bistabile se obt¸ine o secvent¸˘a de num˘ararea de lungime maxim˘a 2

N

− 1. Starea 000...0 este o stare de

blocare.

- Nu orice polinom produce secvent¸e de num˘arare de lungime maxim˘a.

ˆ

In funct¸ie de polinomul ales, se pot obt¸ine mai

multe secvent¸e de num˘arare de lungimi mai mici decˆat lungimea maxim˘a.

- Un circuit LFSR poate fi considerat un generator de numere pseudo-aleatorii, dac˘a are o secvent¸˘a de num˘arare

foarte lung˘a (num˘ar mare de bit¸i) ¸si se utilizeaz˘a un num˘ar mic de e¸santioane succesive.

Figura 17.7 Circuit LFSR pe baza polinomului X

4

+ X

3

+ 1.

17.2. Pentru cei ce vor doar s˘a promoveze examenul 231

17.2 Pentru cei ce vor doar s˘a promoveze examenul

1. Un registru de 4 bit¸i avˆand init¸ial cont¸inutul 1011 este deplasat spre stˆanga secvent¸ial, primind pe intrarea de

date serial˘a secvent¸a 1010111. Precizat¸i cont¸inutul registrului dup˘a fiecare front activ de ceas.

Solut¸ie

Starea viitoare a bit¸ilor registrului este:

Q

+

3

= Q

2

Q

+

2

= Q

1

Q

+

1

= Q

0

Q

+

0

= In

Cont¸inutul registrului dup˘a fiecare front activ de ceas, ˆın funct¸ie de intrarea de date, este redat ˆın tabelul:

Tact Intrare Stare registru

In Q

3

Q

2

Q

1

Q

0

1 1 1 0 1 1

2 0 0 1 1 1

3 1 1 1 1 0

4 0 1 1 0 1

5 1 1 0 1 0

6 1 0 1 0 1

7 1 1 0 1 1

8 - 0 1 1 1

2. Un registru serial de 4 bit¸i se afl˘a init¸ial ˆın starea 0001 ¸si prime¸ste pe intrarea serial˘a secvent¸a 101110011 (cel

mai din stˆanga bit primul). Care este starea registrului dup˘a fiecare front de ceas, ˆın cazul unei deplas˘ari spre

dreapta?

3. Proiectat¸i cu port¸i ¸si bistabile un num˘ar˘ator sincron de 4 bit¸i.

17.3 Pentru cei ce vor s˘a ˆınvet¸e

1. Determinat¸i secvent¸a de num˘arare a circuitului din figura 17.8, indiferent de starea init¸ial˘a.

Figura 17.8 Num˘ar˘ator, problema 1.

Solut¸ie

Circuitul este un num˘ar˘ator ˆın sens descresc˘ator cu facilitate de presetare. Condit¸ia de preset este activ˘a ˆın

starea Q

[3:0]

= 0100|

2

= 4|

10

(conform leg˘aturilor port¸ii AND). Starea de presetare este D

[3:0]

= 1001|

2

= 9|

10

(conform valorilor logice aplicate pe intr˘arile D).

Rezult˘a c˘a circuitul va cicla ˆıntre st˘arile 9, 8, 7, 6, 5, 4. Dac˘a num˘ar˘atorul se va afla ˆın celelalte st˘ari, condit¸ia de

presetare va fi inactiv˘a, deci num˘ar˘atorul va num˘ara ˆın sens descresc˘ator.

Rezult˘a secvent¸a: 3, 2, 1, 0, 15, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 9, 8, .... Se remarc˘a faptul c˘a st˘arile care nu apart¸in

ciclului de num˘arare ar putea s˘a apar˘a doar dup˘a init¸ializare (figura 17.9).

232 LECT¸ IA 17. Registre ¸si num˘ar˘atoare

Figura 17.9 Graf de tranzit¸ii al num˘ar˘atorului, problema 1.

2. Completat¸i diagramele temporale asociate circuitului prezentat ˆın figura 17.10-a.

a) b)

Figura 17.10 a) Circuit propus la problema 2. b) Forme de und˘a ale circuitului.

Solut¸ie

Se observ˘a c˘a num˘ar˘atorul ˆın sens descresc˘ator se ˆınc˘arc˘a cu valoarea binar˘a 10|

2

de fiecare dat˘a cˆand ajunge

ˆın starea 00|

2

. Deci, secvent¸a de num˘arare este: 00, 10, 01, 00, 10, 01, .... Ie¸sirea num˘ar˘atorului este conectat˘a la

select¸ia demultiplexorului, ceea ce ˆınseamn˘a c˘a vor fi activate ciclic ie¸sirile Y

2

, Y

1

¸si Y

0

. Formele de und˘a ale

semnalelor sunt prezentate ˆın figura 17.10-b.

3. S˘a se determine secvent¸a de num˘arare a circuitelor prezentate ˆın figura 17.11. Presupunet¸i starea init¸ial˘a 0.

Studiat¸i cum evolueaz˘a circuitele pornind din toate st˘arile.

a) b)

Figura 17.11 Circuitele de num˘arare propuse la problema 3.

4. Proiectat¸i cu port¸i ¸si bistabile un registru de 4 bit¸i cu facilit˘at¸i de preˆınc˘arcare (dac˘a LD = 1) ¸si deplasare

stˆanga (dac˘a LD = 0 ¸si SH = 1). Dac˘a intr˘arile de control sunt inactive (LD = SH = 0) circuitul ˆı¸si p˘astreaz˘a

starea.

Solut¸ie

Circuitul este format din 4 bistabile. La intrarea acestora se afl˘a circuite multiplexor care selecteaz˘a datele

ˆınc˘arcate pe baza intr˘arilor de select¸ie. Intrarea LD fiind mai prioritar˘a, se aplic˘a p e multiplexorul mai apropiat

bistabilului. Circuitul rezultat este prezentat ˆın figura 17.12.

17.3. Pentru cei ce vor s˘a ˆınvet¸e 233

Figura 17.12 Circuit propus la problema 4.

5. Proiectat¸i cu multiplexoare ¸si bistabile un registru de 4 bit¸i cu facilit˘at¸ile prezentate ˆın tabelul urm˘ator:

S

1

S

0

Operat¸ia

0 0 p˘astreaz˘a valoarea curent˘a

0 1 deplasare stˆanga cu ˆınc˘arcare serial˘a

1 0 deplasare dreapta cu ˆınc˘arcare serial˘a

1 1 ˆınc˘arcare paralel˘a

6. Proiectat¸i un circuit de generare a unui grup de semnale cu 4 faze, perioad˘a de 50 ns ¸si factor de umplere 1/2

pe baza unui semnal cu frecvent¸˘a de 80 MHz.

Solut¸ie

Perioada ceasului de frecvent¸˘a 80 MHz este 1/80 MHz=12, 5 ns. Perioada semnalului generat este de 4 ori mai

mare (50 ns /12, 5 ns = 4). Deci, o perioad˘a de semnal generat este egal˘a cu 4 perioade de ceas.

Solut¸ia de implementare cont¸ine un num˘ar˘ator de 2 bit¸i, modulo 4, care repet˘a periodic 4 faze. Cele 4 semnale

se pot genera cu un circuit combinat¸ional pe baza st˘arii num˘ar˘atorului conform tabelului de adev˘ar:

Faz˘a Q

1

Q

0

O

0

O

90

O

180

O

270

0 00 0 1 1 0

1 01 0 0 1 1

2 10 1 0 0 1

3 11 1 1 0 0

O

0

= Q

1

O

90

= Q

1

⊕ Q

0

O

180

= Q

1

O

270

= Q

1

⊕ Q

0

Implementarea circuitului este prezentat˘aˆın figura 17.13-a. Acest circuit are dezavantajul c˘a ie¸sirile sunt generate

de un circuit combinat¸ional. Solut¸ia de a genera ie¸sirile direct din bistabile se poate implementa f˘ar˘a port¸i logice

suplimentare obsevˆand c˘a O

0

= Q

1

(bitul cel mai semnificativ al num˘ar˘atorului) iar celelate 3 faze se obt¸in din

ˆıntˆarzierea acestuia printr-o serie de 3 bistabile D (figura 17.13-b). Se remarc˘a faptul c˘a, pentru a se genera

secvent¸ele corecte imediat dup˘a semnalul de reset, bistabilele trebuie init¸ializate la valorile ment¸ionate ˆın figur˘a:

num˘ar˘atorul la 00, iar bistabilele la 110.

7. Proiectat¸i un registru de 4 bit¸i cu facilit˘at¸i de resetare sincron˘a utilizˆand 4 bistabile D ¸si 4 circuite MUX 2:1.

8. Proiectat¸i un num˘ar˘ator de 16 bit¸i cu ˆınc˘arcare paralel˘a utilizˆand 4 num˘ar˘atoare de 4 bit¸i cu interfat¸a descris˘a

ˆın continuare:

234 LECT¸ IA 17. Registre ¸si num˘ar˘atoare

a)

b)

Figura 17.13 Generator de 4 faze: a) implementare cu ie¸siri din circuit combinat¸ional, b) implementare cu ˆıntˆarziere prin

bistabile.

Port Direct¸ie Dimensiune Semnificat¸ie

clk in 1 intrare de ceas

reset in 1 intrare de reset asincron

countUp in 1 intrare de control, activ˘a ˆın 1, num˘arare ˆın sens cresc˘ator

load in 1 intrare de control, ˆınc˘arcare, activ˘a ˆın 1, prioritar˘a fat¸˘a de countUp

din in 4 intrare de date

dout out 4 ie¸sire de date

co out 1 transport de ie¸sire, activ ˆın 1 ˆın cazul num˘ar˘arii din 15 ˆın 0

9. Proiectat¸i un circuit secvent¸ial care genereaz˘a ¸sase semnale periodice cu faze diferite, cu formele de und˘a prezen-

tate ˆın figura 17.14. Proiectat¸i circuitul:

a) doar cu bistabile D,

b) cu num˘ar˘ator ¸si decodificator.

Comparat¸i cele dou˘a solut¸ii de implementare.

Figura 17.14 Semnale posibil de utilizat ca semnale de ceas multi-faz˘a, problema 9.

Solut¸ie

Din formele de und˘a prezentate ˆın figura 17.14 se observ˘a c˘a cele 6 semnale au aceea¸si form˘a de und˘a ¸si difer˘a

doar prin faz˘a (T

i

este identic cu T

i−1

, dar este ˆıntˆarziat cu o perioad˘a de ceas).

a) Implementarea cu bistabile D se bazeaz˘a pe o structur˘a de registru de deplasare stˆanga ˆın inel, cu 6 bistabile,

init¸ializate cu valoarea 000001. Circuitul este prezentat ˆın figura 17.15-a.

Dac˘a bistabilele au doar facilitate de reset (se pot aduce init¸ial, asincron, doar ˆın starea 0), atunci se poate

ad˘auga un circuit combinat¸ional care din starea 000000 va conduce circuitul ˆıntr-o stare dorit˘a. Circuitul din

17.3. Pentru cei ce vor s˘a ˆınvet¸e 235

a)

b)

Figura 17.15 Registru de deplasare ˆın inel a) init¸ializat cu 000001, b) cu init¸ializare ˆın starea 000000 ¸si comutare ˆın starea

000001.

figura 17.15-b este un registru de deplasare stˆanga ˆın inel cu init¸ializare ˆın starea 000000 ¸si comutare ˆın starea

000001.

b) Acelea¸si forme de und˘a pot fi generate de c˘atre un num˘ar˘ator modulo 6 ¸si un decodificator 3:8. Num˘ar˘atorul

va num˘ara ciclic de la 0 la 5. Ie¸sirea num˘ar˘atorului este conectat˘a la intrarea decodificatorului. La ie¸sirile

decodificatorului se obt¸in semnalele cerute. Circuitul este prezentat ˆın figura 17.16.

Figura 17.16 Generator de faze implementat cu num˘ar˘ator ¸si decodificator.

Prima abordare necesit˘a 6 bistabile ¸si nu necesit˘a port¸i logice suplimentare (ˆın cazul bistabilelor cu intr˘ari

asincrone de set ¸si reset). Ie¸sirile circuitului sunt direct din bistabile (recomandat).

A doua schem˘a utilizeaz˘a un num˘ar˘ator de 3 bit¸i, deci s-ar putea spune c˘a sunt necesare doar 3 bistabile.

ˆ

Ins˘a,

ˆın acest caz este necesar˘a logica pentru num˘ar˘ator (circuit de incrementare de 3 bit¸i, circuit de detect¸ie a st˘arii

000 ¸si decodificatorul).

ˆ

In plus, ˆın acest caz, ie¸sirile sunt din circuit combinat¸ional (nerecomandat).

Concluzia este c˘a, de¸si a dou˘a schem˘a pare mai direct˘a ca rezolvare a problemei, prima solut¸ie este atˆat mai

ieftin˘a ca resurse hardware cˆat ¸si mai rapid˘a (ca frecvent¸˘a maxim˘a de operare).

10. Un num˘ar˘ator ˆın inel (Engl. ”ring counter”) utilizeaz˘a N bistabile pentru a obt¸ine un ciclu de num˘arare de

N st˘ari. Structura acestui num˘ar˘ator, figura 17.17, prezint˘a N bistabile D, fiecare avˆand ie¸sirea conectat˘a la

intrarea urm˘atorului bistabil. De obicei, num˘ar˘atorul este init¸ializat cu o valoare avˆand un singur bit egal cu 1.

a) Listat¸i secvent¸a de st˘ari a num˘ar˘atorului ˆın inel pornind de la starea init¸ial˘a 0001.

b) Listat¸i celelalte st˘ari ale num˘ar˘atorului ˆın inel ¸si precizat¸i evolut¸ia acestuia ˆın ipoteza aparit¸iei acestora.

c) Modificat¸i circuitul astfel ˆıncˆat, ˆın ipoteza unei st˘ari din afara ciclului dorit, num˘ar˘atorul s˘a revin˘a ˆın ciclul

proiectat.

11. Proiectat¸i structurile LFSR pe baza polinoamelor: X

4

+ X

3

+ 1, X

2

+ X + 1, X

5

+ X

3

+ 1, X

6

+ X

5

+ 1,

X

9

+ X

5

+ 1. Studiat¸i comportamentul circuitului la aparit¸ia st˘arii de blocare (tot¸i bit¸ii egali cu 0). Propunet¸i

un circuit care s˘a init¸ializeze circuitul ˆıntr-o stare valid˘a. Listat¸i secvent¸a de st˘ari prezentat˘a de circuite. Pentru

236 LECT¸ IA 17. Registre ¸si num˘ar˘atoare

Figura 17.17 Num˘ar˘ator ˆın inel de 4 bit¸i, problema 10.

ultimul circuit, folosit¸i calculatorul pentru determinarea secvent¸ei.

Solut¸ie

Circuitele LFSR au o structur˘a de registru de deplasare: intrarea unui bistabil asociat unui bit provine de

la ie¸sirea bistabilului asociat bit-ului mai semnificativ. Intrarea celui mai semnificativ bit provine de la un

circuit logic combinat¸ional implementat cu o poart˘a XOR cu intr˘arile conectate la ie¸sirile bistabilelor, conform

polinomului. Num˘arul de bistabile este egal cu puterea cea mai mare a variabilei ˆın polinom. Circuitele LFSR

asociate p olinoamelor sunt prezentate ˆın figura 17.18.

a) b)

Figura 17.18 Circuit LFSR p e baza polinomelor: a) X

2

+ X + 1, b) X

6

+ X

5

+ 1 .

ˆ

In cazul ˆın care toate bistabile se afl˘a ˆın starea 0, starea viitoare va fi aceea¸si. Circuitul nu va mai putea p˘ar˘asi

aceast˘a stare. Pentru init¸ializarea circuitului ˆıntr-o stare valid˘a, cel put¸in un bistabil va trebui adus ˆın starea 1

printr-un semnal extern de reset. Secvent¸a generat˘a de circuitul LFSR pe baza polinomului X

2

+ X + 1 este:

nr. Z

[1:0]

1 01

2 10

3 11

Secvent¸a generat˘a de circuitul LFSR pe baza polinomului X

5

+ X

3

+ 1 este:

nr. Z

[4:0]

nr. Z

[4:0]

nr. Z

[4:0]

nr. Z

[4:0]

1 00001 9 01110 17 11100 25 10110

2 10000 10 10111 18 11110 26 01011

3 01000 11 11011 19 11111 27 00101

4 10100 12 01101 20 01111 28 10010

5 01010 13 00110 21 00111 29 01001

6 10101 14 00011 22 10011 30 00100

7 11010 15 10001 23 11001 31 00010

8 11101 16 11000 24 01100

12. Studiat¸i comportamentul circuitelor LFSR caracterizate de p olinoamele: X

3

+X

2

+1, X

4

+X

2

+1, X

5

+X

2

+1.

13. Implementat¸i cu bistabile D/T/JK un num˘ar˘ator modulo 6/10/16 cu intrare de validare.

Implementat¸i acela¸si num˘ar˘ator utilizˆand un num˘ar˘ator de 4 bit¸i cu presetare.

Implementat¸i un circuit capabil s˘a numere modulo 6 sau 10 sau 16, num˘arul fiind stabilit pe baza unui cod de

2 bit¸i.

17.3. Pentru cei ce vor s˘a ˆınvet¸e 237

14. Implementat¸i automatele descrise de organigramele din figura 17.19 cu num˘ar˘atoare presetabile.

a) b) c)

Figura 17.19 Organigrame ce descriu automate recomandate a fi implementate cu num˘ar˘ator.

Solut¸ie

Registrul de stare este implementat cu un num˘ar˘ator. Num˘ar˘atorul are dou˘a facilit˘at¸i: s˘a determine prin

incrementare starea urm˘atoare sau s˘a fie ˆınc˘arcat cu o anumit˘a stare din exterior. Pe baza organigramei, se

determin˘a funct¸ia executat˘a de num˘ar˘ator ˆın fiecare stare: num˘arare sau ˆınc˘arcare.

ˆ

In cazul ˆınc˘arc˘arii, trebuie

asigurat˘a existent¸a pe intr˘arile de date ale num˘ar˘atorului a codului st˘arii urm˘atoare. Structura automatului

implementat cu num˘ar˘ator este prezentat˘a ˆın figura 17.20.

Figura 17.20 Structur˘a de automat implementat cu num˘ar˘ator.

Beneficiile implement˘arii cu num˘ar˘ator sunt vizibile ˆın cazul organigramelor care au majoritatea tranzit¸iilor

necondit¸ionate ˆıntre st˘ari cu coduri ordonate ˆın sensul de num˘arare.

ˆ

In acest caz, circuitul care determin˘a logica

semnalului de ˆınc˘arcare ¸si a valorilor de presetare va fi de mici dimensiuni.

15. Implementat¸i cu bistabile D ¸si multiplexoare un registru care s˘a funct¸ioneze conform tabelului:

238 LECT¸ IA 17. Registre ¸si num˘ar˘atoare

SH LD Operat¸ie

1 - deplasare stˆanga

0 1 ˆınc˘arcare paralel˘a

0 0 p˘astreaz˘a starea

16. Implementat¸i cu bistabile D ¸si multiplexoare un registru care s˘a funct¸ioneze conform tabelului:

S

1

S

0

Operat¸ie

0 0 p˘astreaz˘a starea

0 1 resetare sincron˘a

1 0 deplasare dreapta

1 1 ˆınc˘arcare paralel˘a

17. Implementat¸i cu bistabile D ¸si multiplexoare un registru care s˘a funct¸ioneze conform tabelului:

EN LD SH CNT SENS Operat¸ie

0 - - - - p˘astreaz˘a starea

1 1 - - - ˆınc˘arcare paralel˘a

1 0 1 - 1 deplasare dreapta

1 0 1 - 0 deplasare stˆanga

1 0 0 1 1 decrementare

1 0 0 1 0 incrementare

1 0 0 0 - p˘astreaz˘a starea

18. Proiectat¸i un circuit LFSR pe baza unui polinom parametrizabil.

Solut¸ie

Circuitul este format dintr-un registru de deplasare. Intrarea celui mai semnificativ bit se determin˘a pe baza

st˘arii curente ¸si a polinomului caracteristic. Coeficient¸ii polinomului sunt intr˘ari ˆın circuit. Fiecare bit de stare

intr˘a ˆın conjunct¸ie cu coeficientul cu indice corespunz˘ator.

19. Utilizat¸i un num˘ar˘ator presetabil de 4 bit¸i p entru a implementa un num˘ar˘ator BCD (ˆıntre 0 ¸si 9).

20. Justificat¸i valoarea de adev˘ar a fiec˘arei afirmat¸ii:

a) Un num˘ar˘ator de 4 bit¸i are 8 st˘ari valide.

b) Un circuit LFSR de 4 bit¸i are ˆıntotdeauna un ciclu de lungime 15 ¸si o stare de blocare.

Solut¸ie

a) Un num˘ar˘ator de 4 bit¸i are 2

4

= 16 st˘ari valide, deci afirmat¸ia este fals˘a.

21. Care este num˘arul minim de bistabile necesar pentru implementarea unui num˘ar˘ator modulo 10

4

?

a) 10

b) 12

c) 14

d) 15

e) 16

Solut¸ie

10

4

= 10000 < 16384 = 2

14

, rezult˘a ca sunt necesari 14 bit¸i pentru a codifica cele 10

4

st˘ari. Deci, r˘aspunsul

corect este c).

22. Care este deosebirea de implementare a unui reset asincron fat¸˘a de un reset sincron?

23. Care este num˘arul maxim de st˘ari ˆıntr-un ciclu pentru un circuit LFSR de 10 bit¸i?

24. Cˆate bistabile trebuie s˘a comute la schimbarea st˘arii unui num˘ar˘ator dac˘a starea curent˘a este:

a) 01101111, b) 01101101, c) 01011111, d) 01111110.

17.4. Pentru cei ce vor s˘a devin˘a profesioni¸sti 239

17.4 Pentru cei ce vor s˘a devin˘a profesioni¸sti

Registru paralel (cod Verilog)

input[7:0] Dff;

reg[7:0] Qff;

always @(posedge ck)

Qff <= Dff;

Registru paralel-paralel cu intrare de ˆınc˘arcare (cod Verilog)

input[7:0] Dff;

reg[7:0] Qff;

always @(posedge ck)

if (load) Qff <= Dff;

Registru paralel cu reset asincron (cod Verilog)

input[7:0] Dff;

reg[7:0] Qff;

always @(posedge ck or posedge resetAsync)

if (resetAsync) Qff <= ’b0; else

Qff <= Dff;

Registru paralel cu reset sincron (cod Verilog)

input[7:0] Dff;

reg[7:0] Qff;

always @(posedge ck)

if (resetSync) Qff <= ’b0; else

Qff <= Dff;

Registru paralel cu reset sincron ¸si asincron (cod Verilog)

input[7:0] Dff;

reg[7:0] Qff;

always @(posedge ck or posedge resetAsync)

if (resetAsync) Qff <= ’b0; else

if (resetSync) Qff <= ’b0; else

Qff <= Dff;

Registre paralel-serie (cod Verilog)

input[7:0] Dff;

reg[7:0] Qff;

always @(posedge ck or posedge resetAsync)

if (resetAsync) Qff <= ’b0; else

if (load) Qff <= Dff; else

if (shr) Qff <= (Qff >> 1);

assign serialOut = Qff[0];

Registre serie-paralel (cod Verilog)

input[7:0] Dff;

reg[7:0] Qff;

always @(posedge ck or posedge resetAsync)

if (resetAsync) Qff <= ’b0; else

if (load) Qff <= {Qff[6:0], serialIn};

240 LECT¸ IA 17. Registre ¸si num˘ar˘atoare

Registre serie-serie (cod Verilog)

input[7:0] Dff;

reg[7:0] Qff;

always @(posedge ck or posedge resetAsync)

if (resetAsync) Qff <= ’b0; else

if (load) Qff <= {Qff[6:0], serialIn};

assign serialOut = Qff[7];

1. Un num˘ar˘ator Johnson (Engl. ”Johnson counter”) utilizeaz˘a N bistabile pentru a obt¸ine un ciclu de num˘arare

de 2 × N secvent¸e. Structura acestui num˘ar˘ator, figura 17.21, este similar˘a cu a num˘ar˘atorului ˆın inel, prezint˘a

N bistabile D, fiecare avˆand ie¸sirea conectat˘a la intrarea urm˘atorului bistabil, cu except¸ia unui bistabil care

utilizeaz˘a ie¸sirea inversat˘a. De obicei, num˘ar˘atorul este init¸ializat cu o valoare avˆand tot¸i bit¸ii egali cu 0. La

fiecare comutare, bitul mai put¸in semnificativ este negat ¸si reintrodus la intrarea lant¸ului de bistabile.

Figura 17.21 Num˘ar˘ator Johnson de 4 bit¸i, problema 1.

a) Listat¸i secvent¸a de st˘ari a num˘ar˘atorului ˆın inel pornind de la starea init¸ial˘a 0000.

b) Listat¸i celelalte st˘ari ale num˘ar˘atorului ˆın inel ¸si precizat¸i evolut¸ia acestuia ˆın ipoteza aparit¸iei acestora.

c) Modificat¸i circuitul astfel ˆıncˆat, ˆın ipoteza unei st˘ari din afara ciclului dorit, num˘ar˘atorul s˘a revin˘a ˆın ciclul

proiectat (ˆın urm˘atoarea stare sau ˆıntr-un num˘ar finit de st˘ari). Evaluat¸i solut¸iile din punct de vedere al costului

implement˘arii.

Solut¸ie

a) Secvent¸a de st˘ari pe care num˘ar˘atorul le parcurge pornind din starea 0000 este urm˘atoarea:

0000, 1000, 1100, 1111, 1110, 0111, 0011, 0001, 0000, ...

b) Din totalul de 16 st˘ari posibile r˘amˆan 8 st˘ari care nu fac parte din ciclul dorit al num˘ar˘atorului:

0010, 0100, 0101, 0110, 1001, 1010, 1011, 1101, 0010, ....

Din starea 0010 evolut¸ia este urm˘atoarea:

0010, 1001, 0100, 1010, 1101, 0110, 1011, 0101

Se observ˘a c˘a, ˆın cazul aparit¸iei oric˘arei st˘ari din afara ciclului dorit, num˘ar˘atorul va trece succesiv prin toate

cele 8 st˘ari ¸si nu va reveni la funct¸ionarea dorit˘a.

c) Circuitul are 8 st˘ari ˆın ciclul dorit ¸si 8 st˘ari ˆıntr-un alt ciclu. Pentru a reveni la ciclul proiectat, ˆın cazul

aparit¸iei unei st˘ari nedorite, circuitul trebuie extins cu logic˘a adit¸ional˘a. Dac˘a se dore¸ste ca num˘ar˘atorul s˘a revin˘a

la ciclul normal ˆıntr-un singur tact trebuie s˘a se detecteze toate st˘arile ilegale ¸si s˘a se fort¸eze ca urm˘atoarea stare

s˘a fie una din ciclul valid (de exemplu 0000).

ˆ

In tabelul de adev˘ar s-a notat Clear1 semnalul care detecteaz˘a

aparit¸ia unei st˘ari din afara ciclului. Dac˘a Clear1 = 1 starea urm˘atoare este 0000. Acest lucru este implementat

cu circuitul din figura 17.22-a.

Clear1 = Z

3

· Z

1

· Z

0

+ Z

3

· Z

2

· Z

1

+ Z

3

· Z

2

· Z

1

+ Z

3

· Z

1

· Z

0

Dac˘a se dore¸ste ca num˘ar˘atorul s˘a revin˘a la ciclul normal, dar nu neap˘arat ˆıntr-un singur tact, va trebui s˘a se

detecteze o singur˘a stare ilegal˘a (de exemplu, 0010) ¸si s˘a se fort¸eze ca urm˘atoarea stare s˘a fie una din ciclul

valid (de exemplu 0000). Revenirea se va obt¸ine ˆın maximum 8 tacte, presupunˆand c˘a num˘ar˘atorul este init¸ial

ˆın starea 1001 ¸si parcurge tot ciclul alternativ.

ˆ

In tabelul de adev˘ar s-a notat Clear semmnalul care detecteaz˘a

aparit¸ia st˘ari 1001 (din afara ciclului). Dac˘a Clear = 1 starea urm˘atoare este 0000. Acest lucru este implementat

cu circuitul din figura 17.22-b.

Clear = Z

3

· Z

2

· Z

1

· Z

0

17.4. Pentru cei ce vor s˘a devin˘a profesioni¸sti 241

Z

3

Z

2

Z

1

Z

0

Clear1 Clear

0 0 0 0 0 0

0 0 0 1 0 0

0 0 1 0 1 1

0 0 1 1 0 0

0 1 0 0 1 0

0 1 0 1 1 0

0 1 1 0 1 0

0 1 1 1 0 0

1 0 0 0 0 0

1 0 0 1 1 0

1 0 1 0 1 0

1 0 1 1 1 0

1 1 0 0 0 0

1 1 0 1 1 0

1 1 1 0 0 0

1 1 1 1 0 0

a)

b)

Figura 17.22 Num˘ar˘ator Johnson de 4 bit¸i cu revenire ˆın cadrul ciclului a) ˆıntr-un tact, b) ˆın maximum 8 tacte (problema 1).

A doua solut¸ie necesit˘a un circuit combinat¸ional mai simplu, ˆıns˘a determin˘a revenirea ˆın ciclul necesar ˆın maxim

8 perioade de ceas. Prima solut¸ie permite revenirea ˆın ciclul necesar ˆıntr-o singur˘a perioad˘a de ceas, ˆıns˘a utilizˆand

o logic˘a mai complex˘a (posibil cu o frecvent¸˘a maxim˘a mai joas˘a).

2. Utilizat¸i un num˘ar˘ator presetabil de 4 bit¸i pentru a implementa un num˘ar˘ator ˆıntre 3 ¸si 10.

3. Utilizat¸i un num˘ar˘ator presetabil de 4 bit¸i pentru a implementa un num˘ar˘ator ˆıntre dou˘a valori min ¸si max

parametrizabile. Valorile min ¸si max sunt intr˘ari de cˆate 4 bit¸i pentru circuitul proiectat.

4. Circuitul din figura 17.23 este un num˘ar˘ator de 4 bit¸i reversibil, presetabil a c˘arui funct¸ionare este descris˘a de

tabelul urm˘ator:

242 LECT¸ IA 17. Registre ¸si num˘ar˘atoare

LD EN UP Q

+

Act¸iune

1 X X D

ˆ

Inc˘arcare

0 1 1 Q+1 Incrementare

0 1 0 Q-1 Decrementare

0 0 X Q Ment¸inere

C

O

(Carry Output) este o ie¸sire activ˘a ˆın 1 generat˘a combinat¸ional:

- cˆand valoarea curent˘a este 15 ¸si num˘ar˘atorul se incrementeaz˘a ¸si

- cˆand valoarea curent˘a este 0 ¸si num˘ar˘atorul se decrementeaz˘a.

Determinat¸i secvent¸a st˘arilor circuitului prezentat, presupunˆand c˘a porne¸ste din starea 0001.

Figura 17.23 Circuitul cu num˘ar˘ator analizat la problema 4.